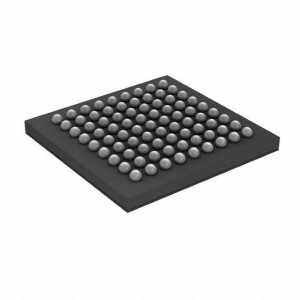

TMS320VC5509AZAY Procesoare și controlere de semnal digital – DSP, DSC Procesor de semnal digital cu punct fix 179-NFBGA -40 până la 85

♠ Descrierea produsului

| Atributul produsului | Valoarea atributului |

| Producător: | Texas Instruments |

| Categorie produs: | Procesoare și controlere de semnal digital - DSP, DSC |

| RoHS: | Detalii |

| Produs: | DSP-uri |

| Serie: | TMS320VC5509A |

| Stil de montare: | SMD/SMT |

| Pachet/Cutie: | NFBGA-179 |

| Miez: | C55x |

| Număr de nuclee: | 1 miez |

| Frecvența maximă a ceasului: | 200 MHz |

| Memoria de instrucțiuni L1 Cache: | - |

| Memoria de date cache L1: | - |

| Dimensiunea memoriei programului: | 64 kB |

| Dimensiunea RAM de date: | 256 kB |

| Tensiune de alimentare de operare: | 1,6 V |

| Temperatura minima de functionare: | -40 C |

| Temperatura maxima de functionare: | + 85 C |

| Ambalare: | Tavă |

| Marca: | Texas Instruments |

| Tip de instrucție: | Punct fix |

| Tip interfață: | I2C |

| Sensibil la umiditate: | da |

| Tip produs: | DSP - Procesoare și controlere de semnal digital |

| Cantitate pachet din fabrică: | 160 |

| Subcategorie: | Procesoare și controlere încorporate |

| Tensiune de alimentare - Max: | 1,65 V |

| Tensiune de alimentare - Min: | 1,55 V |

| Temporizatoare Watchdog: | Timer Watchdog |

♠ Procesor de semnal digital cu punct fix TMS320VC5509A

Procesorul de semnal digital (DSP) TMS320VC5509A se bazează pe nucleul procesorului CPU din generația TMS320C55x DSP.Arhitectura C55x™ DSP atinge performanțe ridicate și putere redusă prin paralelism sporit și concentrare totală pe reducerea disipării puterii.CPU acceptă o structură de magistrală internă care este compusă dintr-o magistrală de program, trei magistrale de citire a datelor, două magistrale de scriere a datelor și magistrale suplimentare dedicate activității periferice și DMA.Aceste magistrale oferă capacitatea de a efectua până la trei citiri de date și două scrieri de date într-un singur ciclu.În paralel, controlerul DMA poate efectua până la două transferuri de date pe ciclu, independent de activitatea CPU.

Procesorul C55x oferă două unități de multiplicare-acumulare (MAC), fiecare capabilă de multiplicare pe 17 biți x 17 biți într-un singur ciclu.O unitate centrală aritmetică/logică (ALU) pe 40 de biți este suportată de o ALU suplimentară de 16 biți.Utilizarea ALU-urilor este sub controlul setului de instrucțiuni, oferind capacitatea de a optimiza activitatea paralelă și consumul de energie.Aceste resurse sunt gestionate în Unitatea de Adresă (AU) și Unitatea de Date (DU) a CPU C55x.

Generația C55x DSP acceptă un set de instrucțiuni cu lățime variabilă de octeți pentru o densitate îmbunătățită a codului.Unitatea de instrucțiuni (IU) efectuează preluări de program pe 32 de biți din memoria internă sau externă și pune în coadă instrucțiuni pentru unitatea de program (PU).Unitatea de program decodifică instrucțiunile, direcționează sarcinile către resursele AU și DU și gestionează conducta complet protejată.Capacitatea de ramificare predictivă evită scăderea conductelor la executarea instrucțiunilor condiționate.

Funcțiile de intrare și ieșire de uz general și A/D de 10 biți oferă suficienți pini pentru stare, întreruperi și I/O biți pentru LCD-uri, tastaturi și interfețe media.Interfața paralelă funcționează în două moduri, fie ca sclav al unui microcontroler folosind portul HPI, fie ca interfață media paralelă folosind EMIF asincron.Media seriale este acceptată prin două periferice MultiMedia Card/Secure Digital (MMC/SD) și trei McBSP.

Setul de periferice 5509A include o interfață de memorie externă (EMIF) care oferă acces fără lipici la memorii asincrone precum EPROM și SRAM, precum și la memorie de mare viteză și densitate, cum ar fi DRAM sincron.Periferice suplimentare includ Universal Serial Bus (USB), ceas în timp real, timer watchdog, I2C multi-master și interfață slave.Trei porturi seriale cu tampon multicanal full-duplex (McBSP) oferă interfață fără lipici la o varietate de dispozitive seriale standard din industrie și comunicație multicanal cu până la 128 de canale activate separat.Interfața îmbunătățită pentru portul gazdă (HPI) este o interfață paralelă pe 16 biți utilizată pentru a oferi procesorului gazdă acces la 32K octeți de memorie internă pe 5509A.HPI poate fi configurat fie în modul multiplexat, fie în modul nemultiplexat pentru a oferi interfață fără lipici unei game largi de procesoare gazdă.Controlerul DMA oferă mișcarea datelor pentru șase contexte de canale independente fără intervenția CPU, oferind un proces DMA de până la două cuvinte de 16 biți pe ciclu.Sunt incluse, de asemenea, două temporizatoare de uz general, până la opt pini I/O de uz general (GPIO) și generarea de ceasuri cu buclă blocată în fază digitală (DPLL).

5509A este susținut de eXpressDSP™, premiat din industrie, Code Composer Studio™ Integrated Development Environment (IDE), DSP/BIOS™, standardul de algoritm al Texas Instruments și cea mai mare rețea terță parte din industrie.Code Composer Studio IDE oferă instrumente de generare a codului, inclusiv un compilator C și Visual Linker, un simulator, drivere de dispozitiv de emulare RTDX™, XDS510™ și module de evaluare.5509A este, de asemenea, susținut de Biblioteca C55x DSP, care conține mai mult de 50 de nuclee software de bază (filtre FIR, filtre IIR, FFT și diverse funcții matematice), precum și biblioteci de suport pentru cip și placă.

Nucleul DSP TMS320C55x a fost creat cu o arhitectură deschisă care permite adăugarea de hardware specific aplicației pentru a crește performanța pe anumiți algoritmi.Extensiile hardware de pe 5509A ating echilibrul perfect între performanța funcției fixe și flexibilitatea programabilă, obținând în același timp un consum redus de energie și un cost care în mod tradițional a fost dificil de găsit pe piața procesoarelor video.Extensiile permit modelului 5509A să ofere performanțe excepționale de codec video, cu mai mult de jumătate din lățimea de bandă disponibilă pentru efectuarea de funcții suplimentare, cum ar fi conversia spațiului de culoare, operațiuni cu interfața utilizator, securitate, TCP/IP, recunoaștere vocală și conversie text în vorbire.Ca rezultat, un singur DSP 5509A poate alimenta majoritatea aplicațiilor video digitale portabile cu spațiu de procesare de rezervă.Pentru mai multe informații, consultați TMS320C55x Hardware Extensions for Image/Video Applications Programmer's Reference (număr de literatură SPRU098).Pentru mai multe informații despre utilizarea Bibliotecii de procesare a imaginilor DSP, consultați Referința programatorului Bibliotecii de procesare imagini/video TMS320C55x (număr de literatură SPRU037).

• Procesor de semnal digital TMS320C55x™, de înaltă performanță, cu putere redusă, cu punct fix

− 9.26-, 6.95-, 5-ns Durata ciclului de instrucțiuni

− Frecvență de ceas de 108, 144, 200 MHz

− Una/două instrucțiuni executate pe ciclu

− Multiplicatori duali [Până la 400 de milioane de multiplicare-acumulare pe secundă (MMACS)]

− Două unități aritmetice/logice (ALU)

− Trei magistrale de citire de date/operanzi interne și două magistrale de scriere de date/operanzi interne

• RAM pe cip de 128K x 16 biți, compusă din:

− 64K octeți de RAM cu acces dublu (DARAM) 8 blocuri de 4K × 16 biți

− 192K octeți de RAM cu acces unic (SARAM) 24 blocuri de 4K × 16 biți

• 64K octeți de ROM pe cip cu o stare de așteptare (32K × 16 biți)

• Spațiu maxim de memorie externă adresabil de 8 M × 16 biți (DRAM sincron)

• Memorie de magistrală paralelă externă pe 16 biți care acceptă:

− Interfață de memorie externă (EMIF) cu capabilități GPIO și interfață fără lipici pentru:

− RAM statică asincronă (SRAM)

− EPROM asincronă

− DRAM sincronă (SDRAM)

− Interfață de porturi gazdă îmbunătățită paralelă pe 16 biți (EHPI) cu capabilități GPIO

• Control programabil la putere redusă a șase domenii funcționale de dispozitive

• Logica de emulare bazată pe scanare pe cip

• Periferice pe cip

− Două temporizatoare pe 20 de biți

− Timer Watchdog

− Controler cu șase canale pentru acces direct la memorie (DMA).

− Trei porturi seriale care acceptă o combinație de:

− Până la 3 porturi seriale cu tampon multicanal (McBSP)

− Până la 2 interfețe MultiMedia/Secure Digital Card

− Generator programabil de ceas în buclă blocată în fază

− Șapte (LQFP) sau opt (BGA) pini I/O de uz general (GPIO) și un pin de ieșire de uz general (XF)

− Port slave USB de viteză completă (12 Mbps) care acceptă transferuri în bloc, întreruperi și izocron

− Interfață Multi-Master și Slave pentru circuite inter-integrate (I2C).

−Ceas în timp real (RTC) cu intrare Crystal, domeniu de ceas separat, sursă de alimentare separată

− Aproximare succesivă A/D cu 4 canale (BGA) sau 2 canale (LQFP) pe 10 biți

• Logica de scanare a limitelor IEEE Std 1149.1† (JTAG).

• Pachete:

− Pachet plat cu 144 de terminale cu profil scăzut (LQFP) (sufix PGE)

− MicroStar BGA™ cu 179 de terminale (Ball Grid Array) (sufixul GHH)

− MicroStar BGA™ cu 179 de terminale fără plumb (Ball Grid Array) (sufix ZHH)

• Core 1,2-V (108 MHz), 2,7-V – 3,6-VI/Os

• Core de 1,35 V (144 MHz), 2,7 V – 3,6 VI/Os

• 1,6-V nucleu (200 MHz), 2,7-V – 3,6-VI/Os

• Sistem hibrid, electric și motor (EV/HEV)

- Sistem de management al bateriei (BMS)

– Încărcător de bord

– Invertor de tracțiune

– Convertor DC/DC

– Starter/generator